A) \[\left| \begin{matrix} A & B & Y \\ 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ \end{matrix} \right|\]

B) \[\left| \begin{matrix} A & B & Y \\ 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \\ \end{matrix} \right|\]

C) \[\left| \begin{matrix} A & B & Y \\ 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ \end{matrix} \right|\]

D) \[\left| \begin{matrix} A & B & Y \\ 0 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \\ \end{matrix} \right|\]

E) \[\left| \begin{matrix} A & B & Y \\ 0 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ \end{matrix} \right|\]

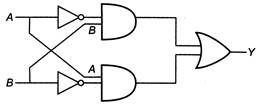

Correct Answer: A

Solution :

Output, \[Y=A\overline{B}+\overline{A}B\] \[\left. \begin{matrix} A=0 & B=0 \\ \overline{A}=1 & \overline{B}=0 \\ \end{matrix} \right]Y=0\] \[\left. \begin{matrix} A=0 & B=1 \\ \overline{A}=1 & \overline{B}=0 \\ \end{matrix} \right]Y=1\] \[\left. \begin{matrix} A=1 & B=0 \\ \overline{A}=0 & \overline{B}=1 \\ \end{matrix} \right]Y=1\] \[\left. \begin{matrix} A=1 & B=1 \\ \overline{A}=0 & \overline{B}=0 \\ \end{matrix} \right]Y=0\] Hence, option (a) is correct.You need to login to perform this action.

You will be redirected in

3 sec