-

question_answer1)

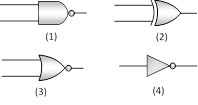

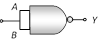

Given below are symbols for some logic gates

The XOR gate and NOR gate respectively are [AFMC 1994]

A)

1 and 2 done

clear

B)

2 and 3 done

clear

C)

3 and 4 done

clear

D)

1 and 4 done

clear

View Solution play_arrow

-

question_answer2)

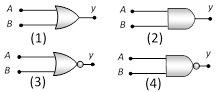

Given below are four logic gate symbol (figure). Those for OR, NOR and NAND are respectively [NSEP 1994]

A)

1, 4, 3 done

clear

B)

4, 1, 2 done

clear

C)

1, 3, 4 done

clear

D)

4, 2, 1 done

clear

View Solution play_arrow

-

question_answer3)

The following truth table corresponds to the logic gate [BHU 1994; CPMT 2000; J & K CET 2004] A 0 0 1 1 B 0 1 0 1 X 0 1 1 1

A)

NAND done

clear

B)

OR done

clear

C)

AND done

clear

D)

XOR done

clear

View Solution play_arrow

-

question_answer4)

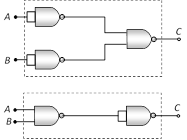

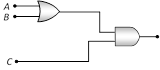

The combination of ?NAND? gates shown here under (figure) are equivalent to [Haryana CEET 1996]

A)

An OR gate and an AND gate respectively done

clear

B)

An AND gate and a NOT gate respectively done

clear

C)

An AND gate and an OR gate respectively done

clear

D)

An OR gate and a NOT gate respectively. done

clear

View Solution play_arrow

-

question_answer5)

A truth table is given below. Which of the following has this type of truth table [CBSE PMT 1996; UPSEAT 2002] A 0 1 0 1 B 0 0 1 1 y 1 0 0 0

A)

XOR gate done

clear

B)

NOR gate done

clear

C)

AND gate done

clear

D)

OR gate done

clear

View Solution play_arrow

-

question_answer6)

The truth table shown in figure is for [Pb. CET 1998] A 0 0 1 1 B 0 1 0 1 Y 1 0 0 1

A)

XOR done

clear

B)

AND done

clear

C)

XNOR done

clear

D)

OR done

clear

View Solution play_arrow

-

question_answer7)

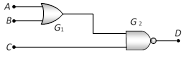

For the given combination of gates, if the logic states of inputs A, B, C are as follows A = B = C = 0 and A = B = 1, C = 0 then the logic states of output\[D\]are [AMU 1998]

A)

0, 0 done

clear

B)

0, 1 done

clear

C)

1, 0 done

clear

D)

1, 1 done

clear

View Solution play_arrow

-

question_answer8)

Boolean algebra is essentially based on [AIIMS 1999]

A)

Truth done

clear

B)

Logic done

clear

C)

Symbol done

clear

D)

Numbers done

clear

View Solution play_arrow

-

question_answer9)

The logic behind ?NOR? gate is that it gives [CPMT 1999, AFMC 1999]

A)

High output when both the inputs are low done

clear

B)

Low output when both the inputs are low done

clear

C)

High output when both the inputs are high done

clear

D)

None of these done

clear

View Solution play_arrow

-

question_answer10)

A logic gate is an electronic circuit which [BHU 2000]

A)

Makes logic decisions done

clear

B)

Allows electrons flow only in one direction done

clear

C)

Works binary algebra done

clear

D)

Alternates between 0 and 1 values done

clear

View Solution play_arrow

-

question_answer11)

A gate has the following truth table [CBSE PMT 2000] P 1 1 0 0 Q 1 0 1 0 R 1 0 0 0 The gate is

A)

NOR done

clear

B)

OR done

clear

C)

NAND done

clear

D)

AND done

clear

View Solution play_arrow

-

question_answer12)

How many NAND gates are used to form an AND gate [MP PET 2004]

A)

1 done

clear

B)

2 done

clear

C)

3 done

clear

D)

4 done

clear

View Solution play_arrow

-

question_answer13)

Which of the following gates will have an output of 1 [CBSE PMT 1998]

A)

B)

C)

D)

View Solution play_arrow

-

question_answer14)

Which represents NAND gate [DCE 2002]

A)

B)

C)

D)

View Solution play_arrow

-

question_answer15)

The given truth table is of [AMU 1998; J & K CET 2002]

A)

OR gate done

clear

B)

AND gate done

clear

C)

NOT gate done

clear

D)

None of above done

clear

View Solution play_arrow

-

question_answer16)

What will be the input of A and B for the Boolean expression \[\overline{(A+B)}\,\cdot \,\overline{(A\cdot B)}=1\] [TNPCEE 2002]

A)

0, 0 done

clear

B)

0, 1 done

clear

C)

1, 0 done

clear

D)

1, 1 done

clear

View Solution play_arrow

-

question_answer17)

If A and B are two inputs in AND gate, then AND gate has an output of 1 when the values of A and B are [TNPCEE 2002]

A)

A = 0, B = 0 done

clear

B)

A = 1, B = 1 done

clear

C)

A = 1, B = 0 done

clear

D)

A = 0, B = 1 done

clear

View Solution play_arrow

-

question_answer18)

The Boolean equation of NOR gate is [Haryana CET 2002]

A)

C = A + B done

clear

B)

\[C=\overline{A+B}\] done

clear

C)

C = A× B done

clear

D)

\[C=\overline{A\cdot B}\] done

clear

View Solution play_arrow

-

question_answer19)

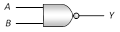

This symbol represents [CBSE PMT 1996]

A)

NOT gate done

clear

B)

OR gate done

clear

C)

AND gate done

clear

D)

NOR gate done

clear

View Solution play_arrow

-

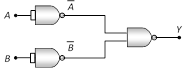

question_answer20)

Which logic gate is represented by following diagram [DCE 2001]

A)

AND done

clear

B)

OR done

clear

C)

NOR done

clear

D)

XOR done

clear

View Solution play_arrow

-

question_answer21)

Symbol

represents [Kerala PMT 2001]

A)

NAND gate done

clear

B)

NOR gate done

clear

C)

NOT gate done

clear

D)

XNOR gate done

clear

View Solution play_arrow

-

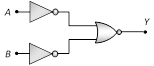

question_answer22)

To get an output 1 from the circuit shown in the figure, the input must be [UPSEAT 2002]

A)

\[A=0,\,\,B=1,\,\,C=0\] done

clear

B)

\[A=1,\,\,B=0,\,\,C=0\] done

clear

C)

\[A=1,\,\,B=0,\,\,C=1\] done

clear

D)

\[A=1,\,\,B=1,\,\,C=0\] done

clear

View Solution play_arrow

-

question_answer23)

The combination of the gates shown in the figure below produces [DCE 2002]

A)

NOR gate done

clear

B)

OR gate done

clear

C)

AND gate done

clear

D)

XOR gate done

clear

View Solution play_arrow

-

question_answer24)

The output of a NAND gate is 0 [UPSEAT 2004]

A)

If both inputs are 0 done

clear

B)

If one input is 0 and the other input is 1 done

clear

C)

If both inputs are 1 done

clear

D)

Either if both inputs are 1 or if one of the inputs is 1 and the other 0 done

clear

View Solution play_arrow

-

question_answer25)

A gate in which all the inputs must be low to get a high output is called [UPSEAT 2004]

A)

A NAND gate done

clear

B)

An inverter done

clear

C)

A NOR gate done

clear

D)

An AND gate done

clear

View Solution play_arrow

-

question_answer26)

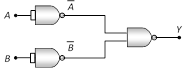

Which logic gate is represented by the following combination of logic gates [AIIMS 2004]

A)

OR done

clear

B)

NAND done

clear

C)

AND done

clear

D)

NOR done

clear

View Solution play_arrow

-

question_answer27)

The output of OR gate is 1 [CBSE PMT 2004]

A)

If both inputs are zero done

clear

B)

If either or both inputs are 1 done

clear

C)

Only if both input are 1 done

clear

D)

If either input is zero done

clear

View Solution play_arrow

-

question_answer28)

Which gates is represented by this figure [DCE 2003]

A)

NAND gate done

clear

B)

AND gate done

clear

C)

NOT gate done

clear

D)

OR gate done

clear

View Solution play_arrow

-

question_answer29)

Sum of the two binary numbers \[{{(1000010)}_{2}}\] and \[{{(11011)}_{2}}\] is [DCE 2004]

A)

\[{{(111101)}_{2}}\] done

clear

B)

\[{{(111111)}_{2}}\] done

clear

C)

\[{{(101111)}_{2}}\] done

clear

D)

\[{{(111001)}_{2}}\] done

clear

View Solution play_arrow

-

question_answer30)

The truth-table given below is for which gate [CBSE PMT 1994, 98 2002; DPMT 2002; BCECE 2005] A 0 0 1 1 B 0 1 0 1 C 1 1 1 0

A)

XOR done

clear

B)

OR done

clear

C)

AND done

clear

D)

NAND done

clear

View Solution play_arrow

-

question_answer31)

Which of the following logic gate is an universal gate [AIIMS 2005]

A)

OR done

clear

B)

NOT done

clear

C)

AND done

clear

D)

NOR done

clear

View Solution play_arrow

![]()

![]()

![]() represents [Kerala PMT 2001]

represents [Kerala PMT 2001]

![]()